# NATIONAL RADIO ASTRONOMY OBSERVATORY Green Bank, West Virginia

Electronics Division Internal Report No. 45

CLOCK AND MARKER SYSTEM

Claude C. Bare

**MARCH 1965**

NUMBER OF COPIES: 75

#### CLOCK AND MARKER SYSTEM

#### Claude C. Bare

#### I. General

This report supersedes the "Clock Master" section (page 2) of Electronics

Division Internal Report No. 34, "Digital Sidereal Clock System".

Local sidereal time is required at most telescopes at NRAO. Two general procedures can be used to provide binary-coded-decimal (BCD) time signals at each telescope.

- 1. Use a standard oscillator at a central location and transmit the standard frequency to all the scopes. The standard frequency is counted at each telescope to provide the BCD signals. This system has the advantage that only a few signals are transmitted to the scopes.

- 2. The system that was chosen uses a standard oscillator and a counter at the central location. The counter provides BCD signals. The counter (clock) BCD outputs are transmitted to all the scopes on a 50 pair telephone cable. Time is standardized for the entire site.

The following signals are provided on the clock cable:

$\Delta T$ (special signal)

0.8 second (BCD)

0.4

0.2

0.1

$0.1\Delta T$

Slow LST marker

Fast LST marker

60 Hertz LST

0.08 second (BCD) LST

Slow EST marker

Fast EST marker

60 Hertz EST

Binary coded decimal EST signals

are available in the clock room

and may be put on the cable later.

Refer to clock cable drawing number 76D000544 for pair color and nomenclature.

#### II. Block Diagram Clock System

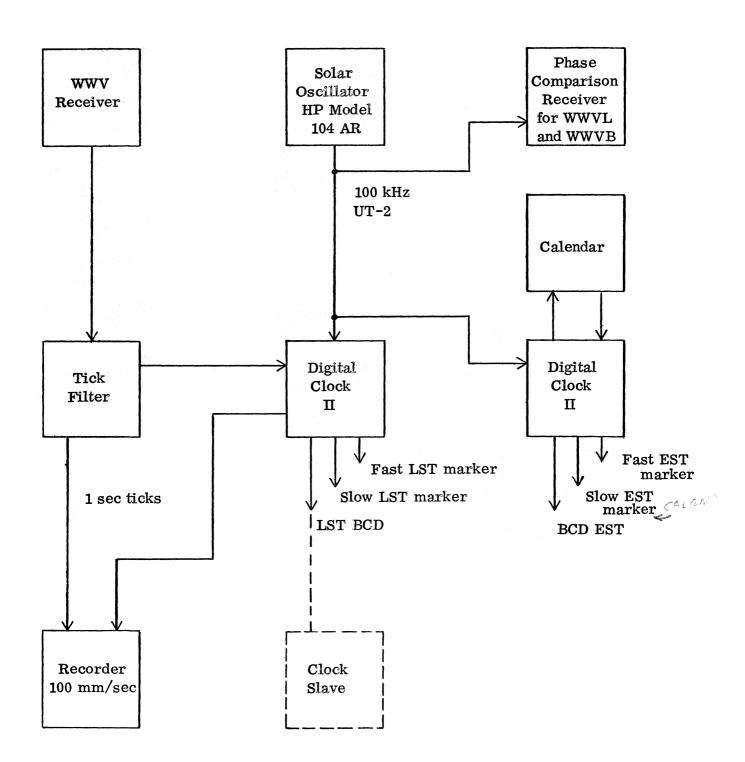

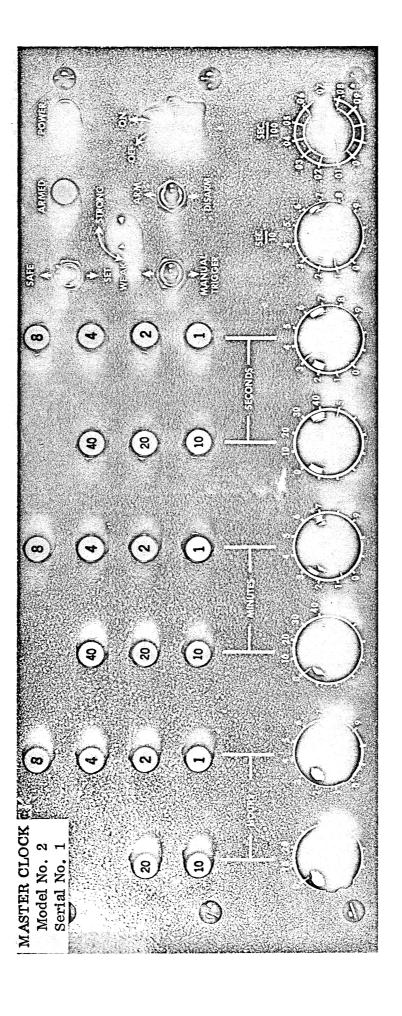

The block diagram of the total system is shown in Figure 1. Notice that a sidereal oscillator is not required and that solar or sidereal time can be provided with the same Digital Clock  $\Pi$ . A photograph of the front panel is included at the end of the report.

#### III. Block Diagram, Digital Clock II

The Digital Clock II is that portion of the clock system with which the author is familiar. This portion will be discussed in detail in the following sections. The following prints are required to follow the discussion of the Digital Clock:

| DL | 650 | Master | Digital | Clock | П |

|----|-----|--------|---------|-------|---|

|----|-----|--------|---------|-------|---|

| DL 561 | 11 | Slow marker                |

|--------|----|----------------------------|

| DL 562 | 11 | Fast marker                |

| DL 563 | 11 | 60 Hertz generator         |

| DL 585 | 11 | Blank printed circuit card |

These drawings are available from the Digital Lab.

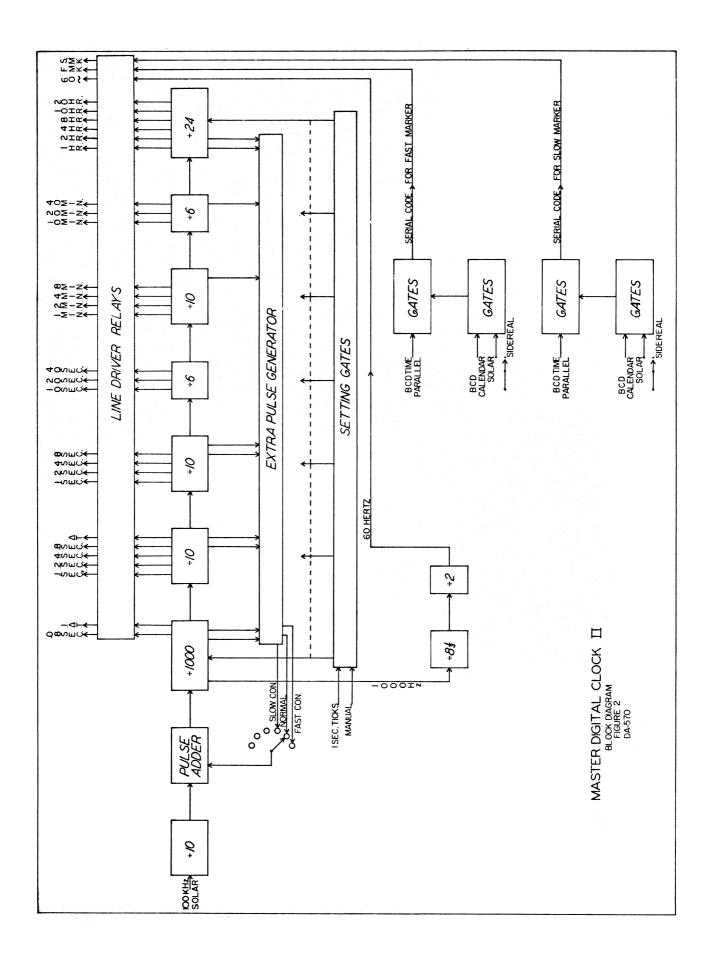

The counter (divider) is the major portion of the digital clock. Refer to Figure 2. Other major sections that will be discussed are:

- 1. Extra pulse generator and pulse adder

- 2. Setting gates

- 3. Serial code markers

- 4. 60 Hertz generator ( $\frac{16}{3}$ )

- 5. Data transmission

- 6. Tick filter (not actually part of Digital Clock II).

The clock can be operated in several modes:

Stop -- used to momentary stop the solar clock.

Solar -- the 100 kc is counted-down without modification.

No conversion sidereal -- a 100 kHz sidereal standard

is counted.

Slow conversion sidereal -- the number of pulses added

to convert to sidereal is re

duced and the clock runs

0.2 percent slow.

Normal conversion sidereal -- the 100 kHz UT-2 solar input is converted to sidereal with an error of 35 microseconds per day  $(error = 4 \times 10^{-10}).$

Fast conversion sidereal -- clock runs 0.3 percent fast.

#### III. Digital Clock II, Counter

The 100 kHz signal from the standard oscillator is counted with BC-20 type Computer Control cards. Refer to logic drawing DL 560. With this portion of the system a solar frequency can be counted to provide solar time or a sidereal frequency can be counted to provide sidereal time. The master clock at NRAO used before 1965 was limited to this type of operation. The major disadvantage of using

a sidereal oscillator is the difficulty of setting the sidereal oscillator to better than a part in 10<sup>5</sup>. A solar oscillator can be set to 1 part in 10<sup>9</sup> in one hour with the Gertch phase-comparison receiver.

## Master Digital Clock II -- Extra Pulse Generator and Pulse Adder

The nominal ratio of a solar day versus a sidereal day is obtained from the following formula:

$$\frac{\text{Mean sidereal day}}{\text{Mean solar day}} = .997269566414 - (0.586 T) x 10^{-10}$$

where T = number of Julian centries of 36525 days of universal time elapsed since the epoch of Greenwich mean noon (regarded as 12 UT) on January 0, 1900.

ratio used in Master Digital Clock II = .997269565973.

The extra pulse generator and pulse adder section provides the hardware for the rate correction. Pulses are added to the 10 kHz solar pulses to bring the average rate up to  $\approx$  10 kHz sidereal. Refer to logic drawing 560. Actually, if a 10 kHz (UT-2) solar rate is applied to the system, the sidereal clock will gain 35  $\mu$ sec per day. The sidereal time will have 1/10 millisec jitter caused by the clock being advanced in 1/10 millisec steps.

The conversion technique is based on the following statements:

- 1. There are .864 x 10<sup>9</sup> tenths of milliseconds in a day.

if the tenths of milliseconds and the day are both

sidereal or both solar.

- 2. In a sidereal day there are 2,359,094.65 less tenths of solar milliseconds in a sidereal day than in a solar day.

- 3. By adding in 2,359,095 pulses during a sidereal day at the 10 kHz part in the counter, the clock will run at approximately a sidereal rate.

- 4. Every flip-flop in the counter goes through a known number of cycles in a day.

- 5. Using the "going true" edge of specific flip-flops to generate extra pulses the number of correction pulses will be correct to the nearest whole number of pulses per day. The 35 μsec error per day represents 35/100 of a correction pulse. Nine correction-pulse flip-flops are required. Refer to the bottom center of DL 560. Table 1 shows the flip-flops used and the number of pulses per day that each provides.

Two other conversion rates are provided in addition to solar to sidereal. On the fast sidereal conversion switch position 2.592 x  $10^{16}$  extra tenths of milliseconds are added per day. This position causes the sidereal clock to advance 3 millisec for each second of time. In the slow position 1.728 x  $10^6$   $\frac{1}{10}$  millisec pulses are lost per day. This causes the sidereal clock to lose 2 milliseconds for each second the switch remains in the slow position. The slow and fast positions are provided to make small corrections in the sidereal clock.

| Extra Pulse Generator | <u>Table 1</u>         |                          |  |

|-----------------------|------------------------|--------------------------|--|

|                       | BCD                    |                          |  |

|                       | weight of              | Number of                |  |

|                       | flip-flop              | cycles/day               |  |

|                       | $\frac{2}{100}$ second | 1,728,000                |  |

|                       | $\frac{1}{10}$ second  | 432,000                  |  |

|                       | $\frac{2}{10}$ second  | 172,800                  |  |

|                       | 2 second               | 17,280                   |  |

|                       | 4 second               | 8,640                    |  |

|                       | 2 minutes              | 288                      |  |

|                       | 10 minutes             | 72                       |  |

|                       | 1 hour                 | 12                       |  |

|                       | 4 hour                 | <u> </u>                 |  |

|                       |                        | 2,359,095 Total          |  |

|                       |                        | - 일반이라면요 시간 없는 것은 사이라는 것 |  |

2,359,094.65 Number desired

#### Master Digital Clock II -- Setting Gates

The clock is set to nearest 1/100 second either with a manual trigger switch or semi-automatically with the tick output from the tick filter. The filter will be explained later. Rotary switches are set to the desired time corresponding to a particular solar minute from WWV. At approximately one second before the minute the circuit is armed and the 60 or 00 tick from WWV will cause the hundredths of seconds and higher order flip-flops of the counter to assume the states specified by the switches. In the absence of a "tick" signal the manual trigger switch may be used.

The quality of the WWV signal will determine the optimum position of the STRONG-WEAK potentiometer. A setting toward STRONG insures that noise will not trigger the auto-set logic, but the WWV tick also may be too weak. This can be adjusted by inhibiting the setting gates with the SAFE switch. Moving a switch to the ARM position causes the ARM LIGHT to burn. The tick signal will cause it to extinguish. When the WWV tick consistently extinguishes the ARM LIGHT but noise does not, the potentiometer is properly adjusted. Moving the SET-SAFE switch to the SET position will cause the clock to be set as the ARM LIGHT is extinguished by the WWV tick. The DISARM position extinguishes the ARM LIGHT without setting the clock. Refer to the photograph at the end of the report for switch location information.

#### Master Clock II -- Serial Code Markers

The parallel BCD outputs are used in the other digital systems, but a different type of output is required for use with Sanborn markers. All the data is required on one line. Therefore, the BCD data is placed on the line in serial with pulse width coding. In addition, ticks (marks) are provided every minute on the slow marker and every ten seconds on the fast marker.

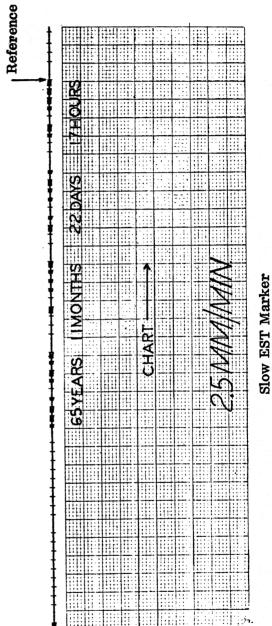

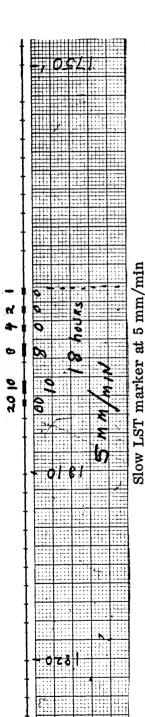

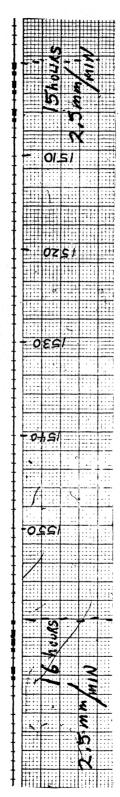

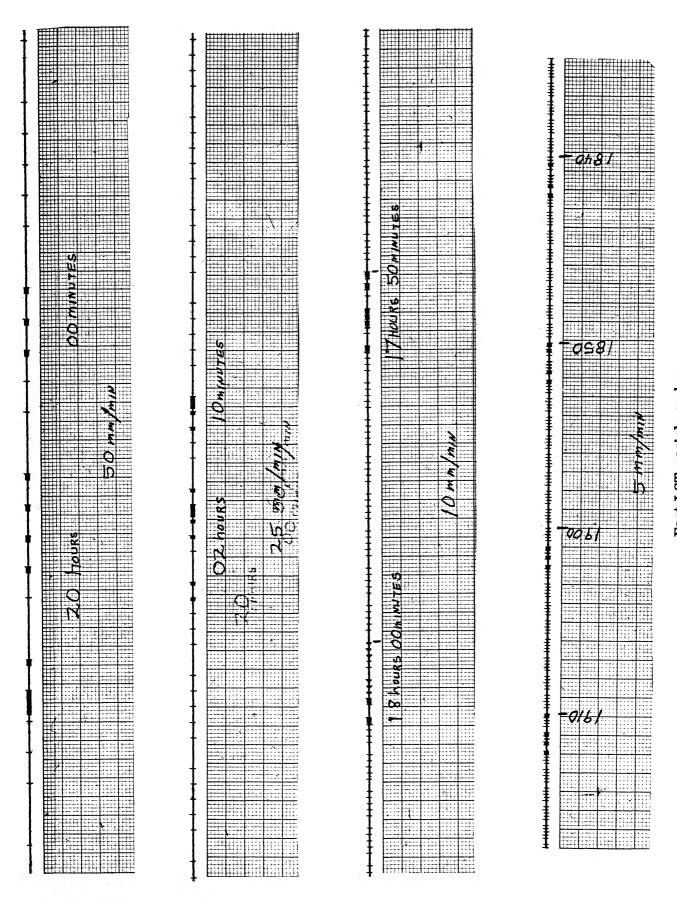

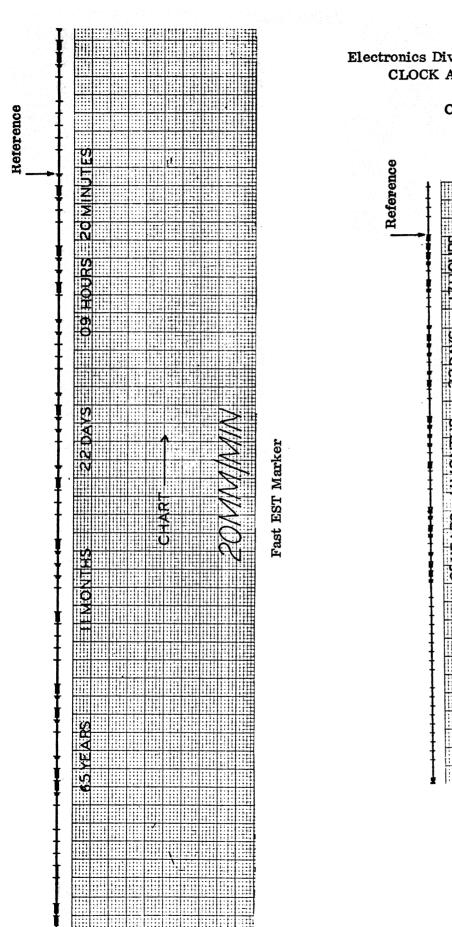

The slow LST marker is shown in Figure 3. At the upper edge of Figure 3A the weight of the individual marker is indicated. Each of these marks corresponds to a BCD bit of data. Since the data is presented only once per hour, only the hours and tens of hours are used. The ticks occur each minute with the exception of the 9th, 19th, 29th, 39th, 49th and 59th minute. The code begins with the least significant

Figure 3A

Slow LST marker at 2.5 mm/min

Figure 3B

Figure 3C

Slow LST marker at 0.5 mm/min

Figure 3D

BCD bit at the beginning of the hour. A logic "one" is 40 seconds long and a logic "zero" is 20 seconds long. The tick is approximately 1/10 second in length.

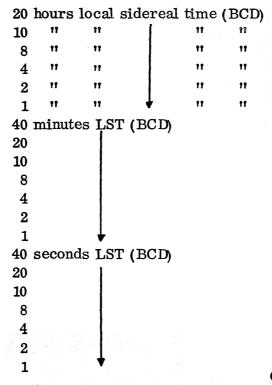

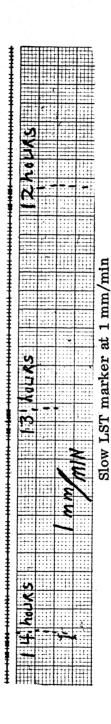

The fast LST marker is shown in Figure 4. The serial time data is presented each 10 minutes. Therefore, tens of minutes are required along with hours and tens of hours. The logic "one" mark is 40 seconds in length, logic "zero" is 20 seconds, and the tick is approximately 1/10 second in length. The time that is referenced by the serial BCD is the beginning time of the least significant bit. The ticks occur each 10 seconds with the tick at 50 seconds omitted.

The fast EST serial marker will contain the following BCD data:

| tens of minutes | during 1st minute  |

|-----------------|--------------------|

| unit hours      | during 2nd minute  |

| tens of hours   | during 3rd minute  |

| unit days       | during 4th minute  |

| tens of days    | during 5th minute  |

| unit of months  | during 6th minute  |

| tens of months  | during 7th minute  |

| unit years      | during 8th minute  |

| tens of years   | during 9th minute  |

| None            | during 10th minute |

The slow EST marker will contain the following BCD data:

| unit hours tens of hours | during first 10 minutes  |

|--------------------------|--------------------------|

| days<br>tens of days     | during second 10 minutes |

| months tens of months    | during third 10 minutes  |

| years tens of years }    | during fourth 10 minutes |

| none                     | during fifth 10 minutes  |

| none                     | during sixth 10 minutes  |

Fast LST serial marker Figure 4

The solar slock may be operated without a calendar. The parallel data will be "zeroes" for days and months and the years will be all "ones" if a calendar is not connected. The existence of "ones" or "zeroes" in the days, months, and years locations is used to differentiate the EST markers from the LST markers. Examples of the EST markers will be supplied on request after the solar clock and calendar are in operation.

### Master Digital Clock II -- 60 Hertz Generator

The 140-foot scope requires 60 Hertz solar and 60 Hertz sidereal. One of these is provided by each Master Digital Clock II. Refer to DL 563. The 60 Hertz signal is provided by dividing the 1 kilo Hertz signal by 8 1/3 and then by 2. The division by 8 1/3 is accomplished by a "divide by 8" followed by a "divide by 3".

Each time the "divide by 3" cycles one pulse is omitted by the "divide by 8" counter.

Therefore, cycles of the "divide by 8" counter are the following lengths:

#### 8 milliseconds

8 1

9

8 1

8 11

9 1

etc.

This signal is divided by two to generate a 60 Hertz signal. The signal is composed of the following length cycles:

#### 16 milliseconds

17

17

16

17

17

etc.

Due to the technique used to generate the 60 Hertz signal, there will be some 1 millisec jitter on the signal. It is not expected that the jitter will be noticeable when driving the clock motors at the 140-foot telescope.

#### Master Digital Clock II -- Data Transmissions

The data is transmitted to the scopes via a 50 pair telephone cable. Refer to drawing 76D000544. The clock logic drives mercury relays (Clare HGS 5015 or PB JML 1160-81) which connect the high side of the lines to + 12 volts for logic "zero" or to -18 volts for a logic "one". In series with the high side of each data pair is a 100 ohm resistor to attenuate line transits and to protect the power sources if a line is shorted. The voltages for the data lines are protected by independent fuses, so that the whole clock will not stop even if the data transmission portion of the system is interrupted. The low side of each data pair is grounded (earthed) at the clock master. The low sides may be connected together to save connectors, but must not be "earthed" at additional locations. Logic drawing DL 560 includes schematics of the relay circuits. Refer to DL 563 for the relay circuit for the 60 Hertz generator.

The -18 to +12 volt signal operates a bi-polar mercury relay (Clare HGS 1114) at each clock slave. The voltage required at each slave is 2.05 volts across 2.5 K ohms. The system was designed to drive 10 slaves with extreme safety. The form D contacts of slave relays are used to provide logic levels (both true and false) to drive displays and other digital equipment at each scope. Refer to the applicable slave drawing:

| 300-foot       | DL 750  |

|----------------|---------|

| 85-2           | DL 1150 |

| 85-1           | DL 2150 |

| Interferometer | DL 2550 |

| 140-foot       | DL 2550 |

#### Tick Filter

The tick filter takes audio from a WWV receiver and removes the noise and other audio tones from the 1 kHz used for time marks. The 1 kHz digital data cannot be removed. Four White "twin-T" filters and two amplifiers are used: 440 Hz as a trap, 1 kHz as a passband amplifier, 660 Hz as a trap, and a 1 kHz as a passband amplifier. Refer to Figure 5 for a block diagram. During periods of no voice and no digital data, the tick filter provides one second signals for setting the clock and to run time checks.

Time checks are recorded on a fast (100 mm/sec) Sanborn recorder. The WWV ticks are compared with a signal from the sidereal clock. The "two second" LST signal is used now, since it is nonambigious over a ten second period. Later a fast EST marker and a fast LST marker will be added to the data recorded. The time (year, month, day, minute) and the WWV UT-2 tick offset are written on the record. The record is reduced with the aid of computed LST to EST tables.

ADDENDUM to

Electronics Division Internal Report No. 45 CLOCK AND MARKER SYSTEM

by Claude C. Bare March 1965