# NATIONAL RADIO ASTRONOMY OBSERVATORY GREEN BANK, WEST VIRGINIA

# ELECTRONICS DIVISION TECHNICAL NOTE NO. 159

Title:

VLBA Monitor and Control Card Application Problems

Author(s): Ronald B. Weimer

Date: March 21, 1990

## **DISTRIBUTION:**

GB GB Library R. Lacasse D. Schiebel E. Childers C. Brockway J. Coe R. Norrod S. White G. Behrens R. Fisher

F. Crews

<u>CV</u> ER Library IR Library M. Balister N. Bailey L. D'Addario N. Horner A. R. Kerr

C. Burgess

S. Srikanth

<u>TU</u> Library Downtown Library Mountain R. Freund P. Jewell J. Lamb <u>VLA</u> VLA Library P. Napier J. Campbell W. Brundage R. Weimer

### VLBA MONITOR AND CONTROL CARD APPLICATION PROBLEMS

#### Ronald B. Weimer

#### Introduction

During the last couple of months two problems have come to light that might be causing other people some trouble. The purpose of this note is to make others aware of these problems and some possible solutions to them. The first one causes the M/C card to select the wrong analog channel when using external multiplexers ahead of the A/D converter. The second problem concerns loading of analog monitor channels under certain conditions.

#### Channel Select Problem

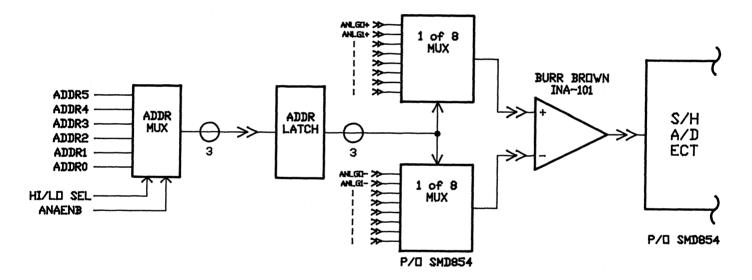

A partial block diagram of the M/C card is shown in Figure 1 below.

### Figure 1

Occasionally when reading premux channels (addresses above 7 hex) the address control circuit would latch in the base address bits (ADDRO-ADDR2) instead of the higher address bits (ADDR3-ADD45). For example, 14H (010100 B) should latch 010 in the A/D mux and select 100 in the external mux. The A/D address latch is controlled by the ANAENB signal and the address to be latched is controlled by the HI/LO SEL signal. Since both of these were generated on the digital card from the address decoders, occasionally the ANAENB would latch data before the digital mux had switched to the high address bits. The solution was to delay the ANAENB signal relative to the HI/LO SEL signal. I used a couple extra inverters in the ANAENB line. A second approach would be to decode address blocks without DEVREQ; use this output for HI/LO SEL and gate DEVREQ with the address blocks to generate ANAENB signal. Address bits are output at least 5 microseconds before the DEVREQ signal is generated.

#### Loading Problems

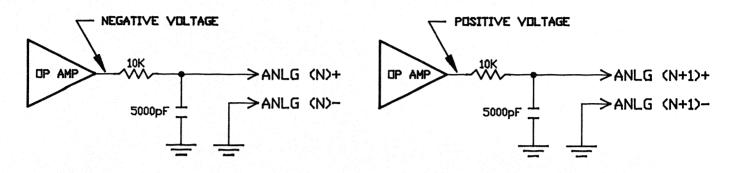

The second problem was noticed by L. Beno on some analog signals monitored from the L104 2 to 16 GHz synthesizer module. If a negative voltage reading was followed by a positive voltage reading, there was considerable error in the positive value. The typical module outputs are shown in Figure 2.

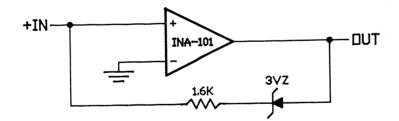

Upon investigation it was found that the positive channel was being loaded down during its read time. The culprit turned out to be the Burr Brown instrumentation amp INA101. (See Figure 1.) Its input impedance is specified at 10E10 ohms typical. Its slew rate is specified at 0.4 V/ $\mu$ s. Slew rate measured 0.36 V/ $\mu$ s on a sample. The slew rate was independent of output capacity loading from 0 to 1000 pF. However, if the step is over approximately +4 volts, the input impedance goes to 1.6 K ohm in series with about 3 volt offset tied to the output. Figure 3 shows a model of the amp input during a positive slew condition.

## Figure 3

Since it takes 55  $\mu$ s to slew 20 volts, there is appreciable discharge of the 5000 pF capacitor. The time constant is around 8  $\mu$ s. The test I made on the op-amp itself did not include the series impedance of the mux in the SMD-854 (1.5 K ohm) which would increase the discharge time constant and reduce the voltage offset. The recharge time constant is 50  $\mu$ s. If the voltage offset were 1 volt, the residual error would be 49 mV after 150  $\mu$ s. The A/D system waits 200  $\mu$ s before sampling the analog channel for conversion. The LSB of the A/D is 5 mV. Larry Beno tested the effect of adding a capacitor in parallel with the 5000 pF feedthru. Tests indicate that at least 0.1  $\mu$ F and preferably 1.0  $\mu$ F cap was needed to reduce the error to an acceptable level.

Another approach would be to reduce the 10 K ohm resistor in Figure 2 to 1.0 K ohm. This would reduce the recharge time constant to 5  $\mu$ s. This would give 30 time constants. I think this would still give adequate decoupling of signals coming in or out of the unit.

One other approach would be to substitute a different op-amp for the Burr Brown INA-101. I talked to an applications engineer at Burr Brown. He was not aware that the 101 did this type of thing and could not suggest a pin compatible replacement. One problem is that the printed circuit is laid out for the 10 pin round can package. Most newer amps come in a dip package. If anyone has a suggestion, please let me know.

RBW/cjd